Past

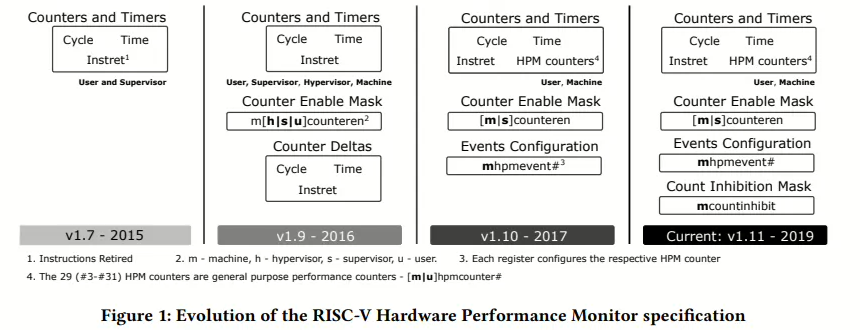

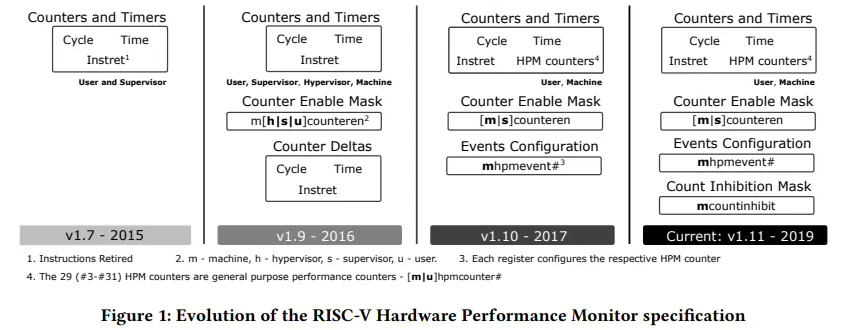

Previous PMU Evolution

Implementation Details

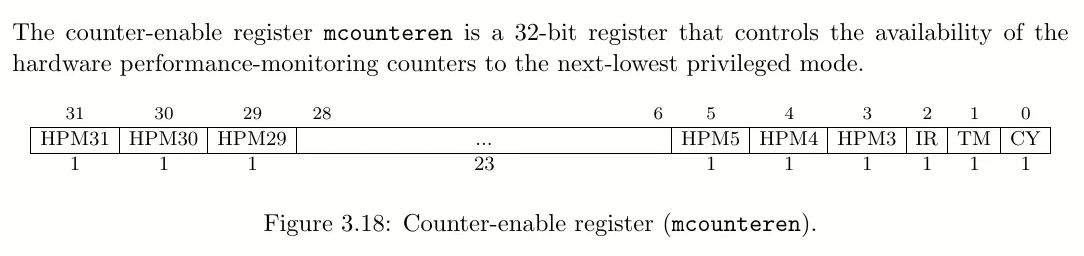

- Privileged spec

- mcounteren, hcounteren, scounteren

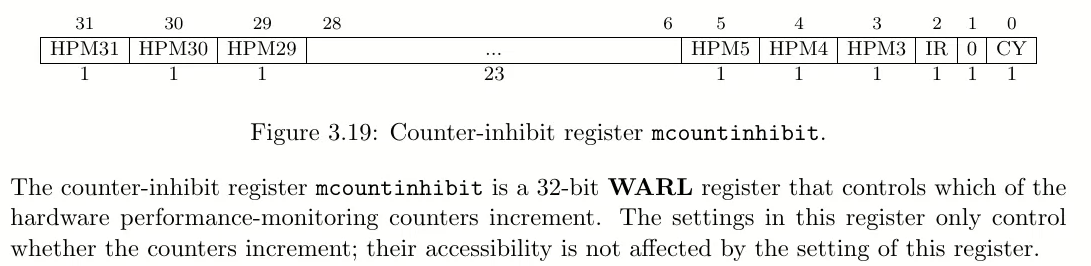

- mcountinhibit

- The cycle, instret, and hpmcountern CSRs are read-only shadows of mcycle, minstret, and mhpmcountern respectively. The time CSR is a read-only shadow of the memory-mapped mtime register.

- 意味着在userspace是可以访问这些csr的,如果scounteren对应位是enabled

- 同样smode也可以读这些counter,如果mcounteren/hcounteren置位,这样就不用切换到M mode来读取这些值

- mhpmevent

- 意味着config(start/stop)只能在M mode操作这些csr

Present

Sscofmpf

- https://github.com/riscv/riscv-count-overflow

CSRs

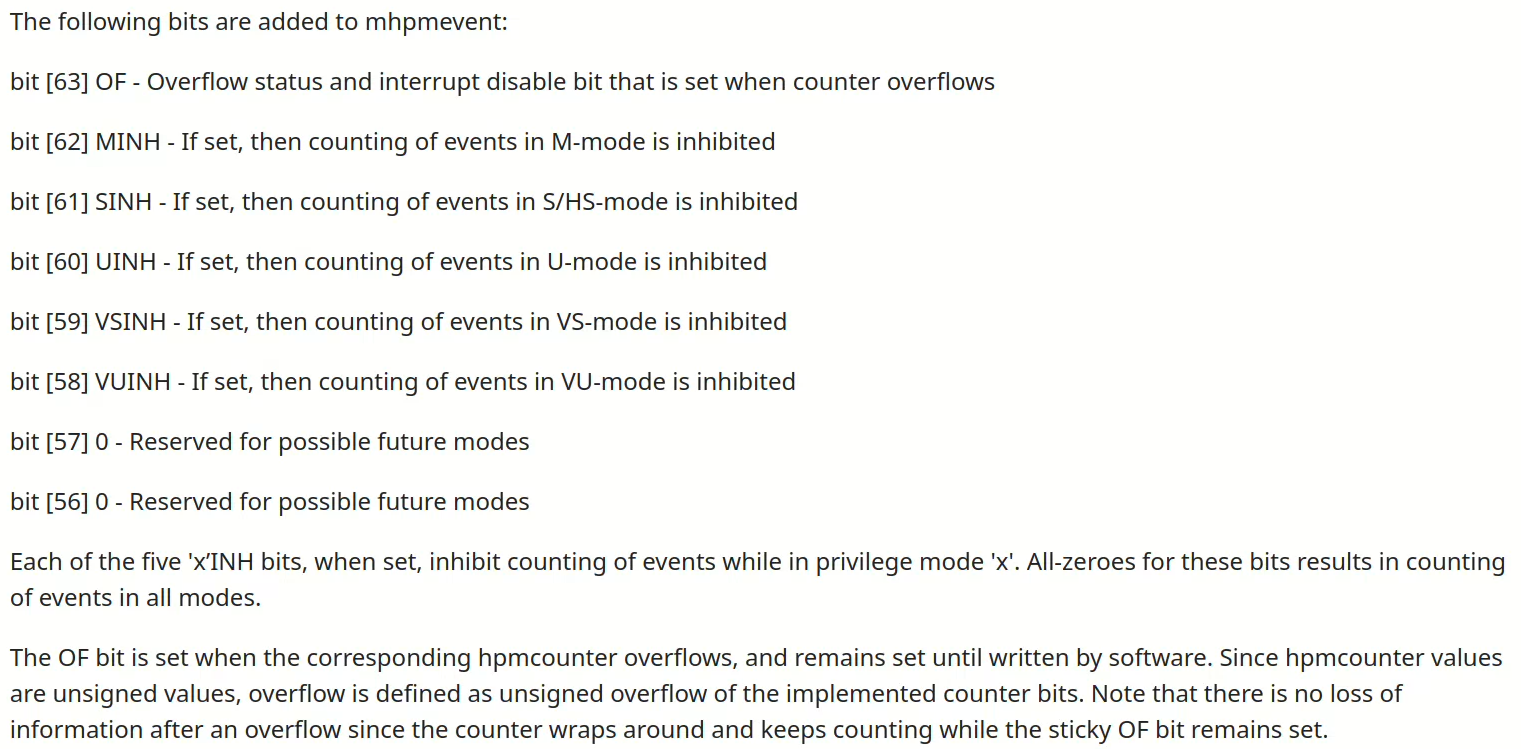

- mhpmevent - reuse the high bits

- mip/mie - LCOFIP is added to mip in Figure 3.14 as bit 13. LCOFIP is added to mie in Figure 3.15 as bit 13.

- sip/sie - LCOFIP is added to sip in Figure 4.6 as bit 13. LCOFIP is added to sie in Figure 4.7 as bit 13.

- 意味着在smode就可以处理overflow中断

- scountovf - The scountovf CSR is a 32-bit read-only register that contains shadow copies of the OF bits in the 29 mhpmevent CSRs (mhpmevent3-mhpmevent31) - where scountovf bit X corresponds to mhpmeventX.

Control Transfer Records (CTR)

可以理解为Intel LBR的riscv版本

- https://github.com/riscv/riscv-control-transfer-records

Smcdeleg/Ssccfg

-

https://github.com/riscv/riscv-smcdeleg-ssccfg

-

For a Machine-level environment, extension Smcdeleg (‘Sm’ for Privileged architecture and Machine-level extension, ‘cdeleg’ for Counter Delegation) encompasses all added CSRs and all behavior modifications for a hart, over all privilege levels.

-

For a Supervisor-level environment, extension Ssccfg (‘Ss’ for Privileged architecture and Supervisor-level extension, ‘ccfg’ for Counter Configuration) provides access to delegated counters, and to new supervisor-level state.

This extension provides a means for M-mode to allow writing select counters and event selectors from S/HS-mode. The purpose is to avert transitions to and from M-mode that add latency to these performance critical supervisor/hypervisor code sections.

The mcounteren register allows M-mode to provide the next-lower privilege mode with read access to select counters. When the Smcdeleg extension is enabled, it further allows M-mode to delegate select counters to S-mode.

SBI SSE

- Stands for Supervisor Software Events

- Used for NMI-like scenario (for perf) and others such as RAS

- Status: relatively early stage

- https://github.com/avpatel/riscv-sbi-doc/tree/sbi-sse-extension-v2

Future

| Intel(x86) | ARM | RISC-V | User Scenarios | Comments |

|---|---|---|---|---|

| TMA (top-down) | Basic | Drill down hotspot | ARM top-down | |

| LBR | BRBE | CTR | AutoFDO | |

| NMI | NMI/SDEI | SBI SSE | Profiling interrupt context | SBI SSE |

| PEBS | SPE | Precise events for memory debugging etc. | False Sharing | |

| PT | CoreSight | E-Trace | Record all branches instructions | |

| Rich PMU events | Rich |

我们期望对一些常见场景比如cache false sharing有快速有效的方法,对相对复杂场景有办法能够深入分析。